La memoria Flash serie W25Q64FV (64 Mbits) proporciona una solución de almacenamiento para sistemas con espacio, pines y energía limitados. La serie 25Q ofrece flexibilidad y rendimiento mucho más allá de los dispositivos Serial Flash ordinarios. Son ideales para emular código en RAM, ejecutar código directamente desde Dual/Quad SPI (XIP) y almacenar voz, texto y datos. El dispositivo funciona con una sola fuente de alimentación de 2,7 V a 3,6 V con un consumo de corriente tan bajo como 4 mA activo y 1 µA para el apagado. Todos los dispositivos se ofrecen en paquetes que ahorran espacio.

La matriz W25Q64FV está organizada en 32 768 páginas programables de 256 bytes cada una. Se pueden programar hasta 256 bytes a la vez. Las páginas se pueden borrar en grupos de 16 (borrado de sector de 4 KB), grupos de 128 (borrado de bloque de 32 KB), grupos de 256 (borrado de bloque de 64 KB) o el chip completo (borrado de chip). El W25Q64FV tiene 2048 sectores borrables y 128 bloques borrables respectivamente. Los pequeños sectores de 4 KB permiten una mayor flexibilidad en aplicaciones que requieren almacenamiento de datos y parámetros.

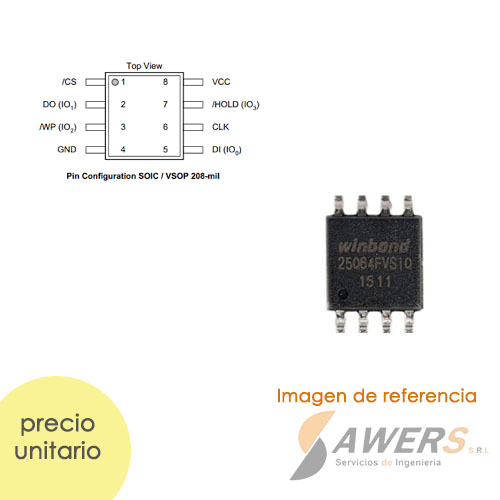

El W25Q64FV admite la interfaz de periféricos en serie (SPI) estándar, SPI de E/S doble/cuádruple, así como la interfaz de periféricos cuádruples (QPI) de ciclo de instrucción de 2 relojes: reloj en serie, selección de chip, E/S de datos en serie (DI), I /O1 (DO), E/S2 (/WP) y E/S3 (/HOLD). Se admiten frecuencias de reloj SPI de hasta 104 MHz, lo que permite velocidades de reloj equivalentes de 208 MHz (104 MHz x 2) para E/S doble y 416 MHz (104 MHz x 4) para E/S cuádruple cuando se usa E/S doble/cuádruple de lectura rápida y QPI instrucciones. Estas velocidades de transferencia pueden superar el rendimiento de las memorias flash paralelas asíncronas estándar de 8 y 16 bits. El modo de lectura continua permite un acceso eficiente a la memoria con tan solo 8 relojes de sobrecarga de instrucciones para leer una dirección de 24 bits, lo que permite una verdadera operación XIP (ejecutar en el lugar). Un pin de retención, pin de protección contra escritura y protección contra escritura programable, con control de matriz superior o inferior, proporcionar una mayor flexibilidad de control. Además, el dispositivo es compatible con la identificación del dispositivo y el fabricante estándar JEDEC, un número de serie único de 64 bits y tres registros de seguridad de 256 bytes.

DATASHEET