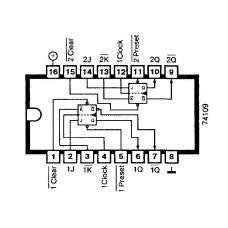

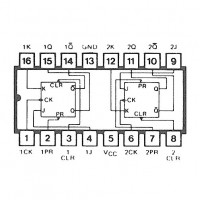

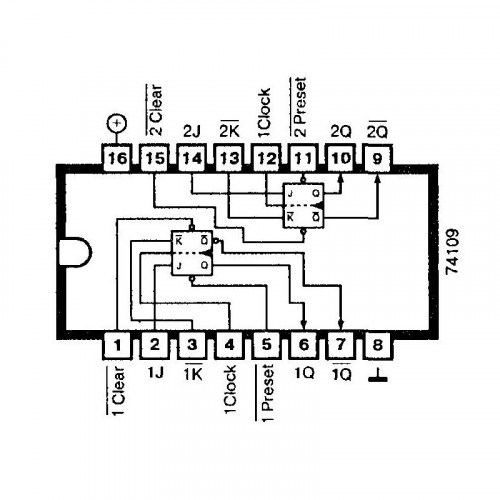

Circuito Integrado TTL 74LS109. Flip flop J-K con borde positivo activado que consta de dos Flip-flop independientes con función cleas y preset . La operación de reloj es independiente de la subida y tiempos de caída de la forma de onda del reloj. El diseño JK permite la operación como un Flip-flop D simplemente conectando el J y el K juntos.

Especificaciones

Familia: LS

Tipo Flip-flop: JK

Tipo de disparo: Edge Positivo

IC Tipo de salida: Differential / Complementaria

Tensión de Alimentación Mín: 4.75 V

Tensión de Alimentación Máx: 5.25 V

Retardo de propagación: 13 ns

Frecuencia: 33 MHz

Corriente de salida: 8 mA

Rango temperatura de funcionamiento: 0A