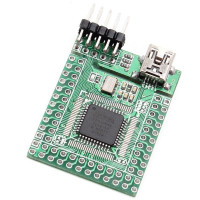

Los CPLD son dispositivos que integran elementos lógicos programables, estos elementos pueden conectarse entre sí o con las salidas GPIO usando una matriz de conexiones programables. A diferencia de los FPGA que generalmente no guardan su configuración y necesitan de otro controlador y componentes externos para iniciarlo, los CPLD si guardan su configuración y está disponible al ser energizados, esto disminuye la complejidad de sus tarjetas y programación. La desventaja frente a los FPGA es que sus bloques programables usualmente tienen menos lógica configurable, a pesar de esto son muy capaces en muchas tareas y proyectos.

Voltaje de alimentación: 5 - 9V DC

Voltaje de operación: 3.3V

CPLD: Altera (Ahora Intel) MAXII EPM240T100C4N

Elementos lógicos: 240

Numero de IO E/S: 80

Entradas/salidas programables para operar a niveles lógicos 3.3 V, 2.5 V, 1.8 V, y 1.5 V

Soporta hasta 150Mhz, oscilador en la placa de 50Mhz

Conector de programación: JTAG

InstantOn, non-volatile storage

Temperatura de funcionamiento: 0-70C

El jumper J2 conecta el led D1 con PIN_77, además el oscilador externo está conectado a la entrada Clock 0 (PIN_12)

Dimensiones: 50x70mm